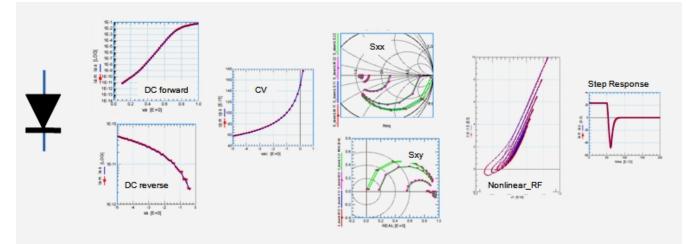

# **DIODE MODELING TUTORIAL** From DC $\rightarrow$ CV $\rightarrow$ S-Parameters $\rightarrow$ Nonlinear-RF $\rightarrow$ Time Domain

#### **Keywords**:

Diode Spice Model, DC Forward and Reverse Modeling, Space Charge and Diffusion Charge Modeling, Nonlinear-RF Modeling and Model Inspection

#### **Contents:**

| Introduction            | 2  |

|-------------------------|----|

| DC Forward Modeling     | 5  |

| DC Reverse Modeling     |    |

| CV Modeling             |    |

| S-Parameter Modeling    |    |

| Nonlinear-RF Inspection | 22 |

| Time-Domain Inspection  | 25 |

| Modeling Result         |    |

| 5                       |    |

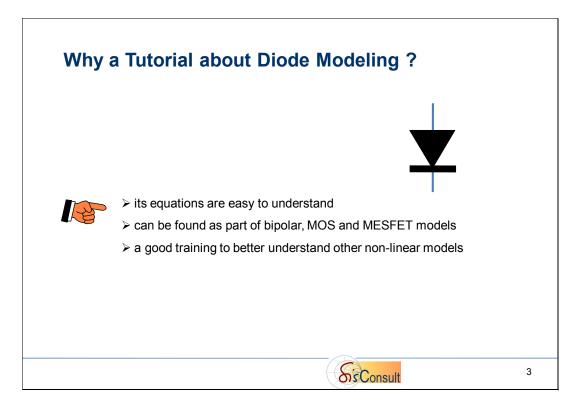

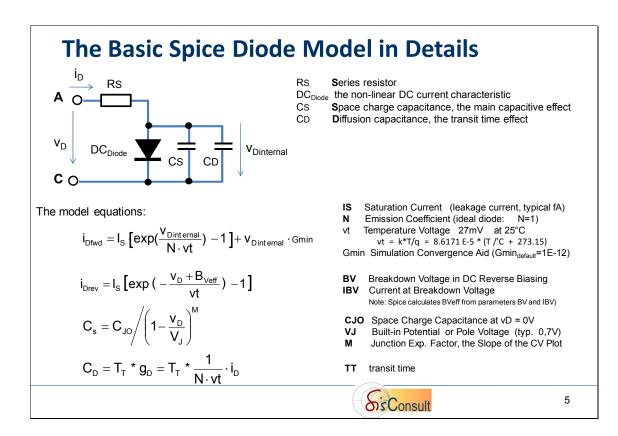

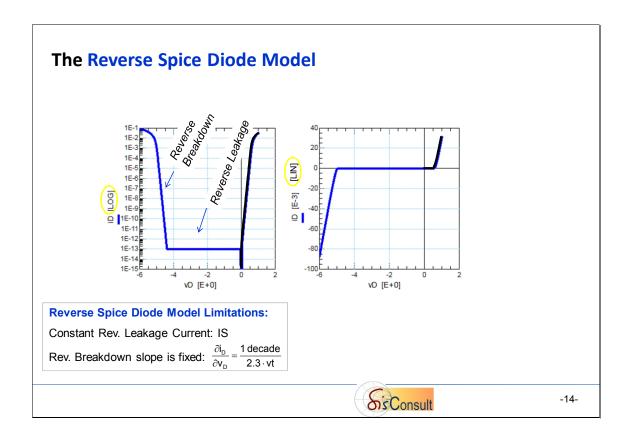

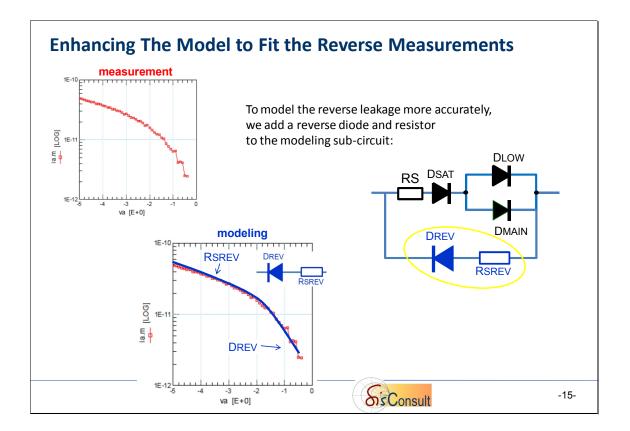

Effects not covered by the standard SPICE diode model are:

- recombination effect (low forward DC bias)

- reverse off-state current between OV and breakdown voltage Note: In practice, this is never simply IS

#### The SPICE Diode Model Parameter List:

| param                | . description                                                                                   | units      | default              | example.                     |

|----------------------|-------------------------------------------------------------------------------------------------|------------|----------------------|------------------------------|

| RS                   | ohmic resistance                                                                                | Ohm        | 0                    | 10                           |

| IS<br>N              | saturation current emission coeff.                                                              | A<br>_     | 1.0E-14<br>1         | 1.0E-14<br>1                 |

| BV<br>IBV            | rev. breakdown volt.<br>current at BV                                                           | V<br>A     | inf.<br>1.E-3        | 40                           |

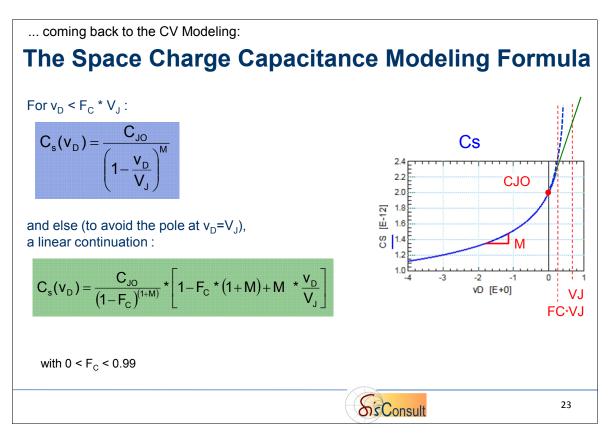

| CJO<br>VJ<br>M<br>FC | zero bias junct. cap.<br>junction potential<br>diffusion grading coeff<br>CJ lin. extens.coeff. | F<br>V<br> | 0<br>1<br>0.5<br>0.5 | 2.0E-12<br>0.6<br>0.5<br>0.5 |

| TT                   | transit time                                                                                    | sec        | 0                    | 1E-10                        |

| EG                   | activation energy                                                                               | eV         | 1.11 for<br>0.67 for | Si<br>Ge                     |

| XTI                  | sat. current temp.exp.                                                                          | -          | 3.0                  | 3                            |

| KF<br>AF             | flicker noise coefficien<br>flicker noise exponent                                              | t –<br>–   | 0<br>1               |                              |

| TNOM                 | modeling temp.                                                                                  | 'C         | 27                   |                              |

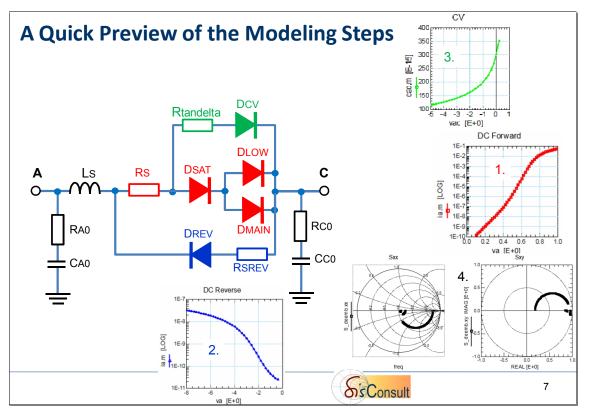

This slide gives a quick preview about what will be covered in this tutorial.

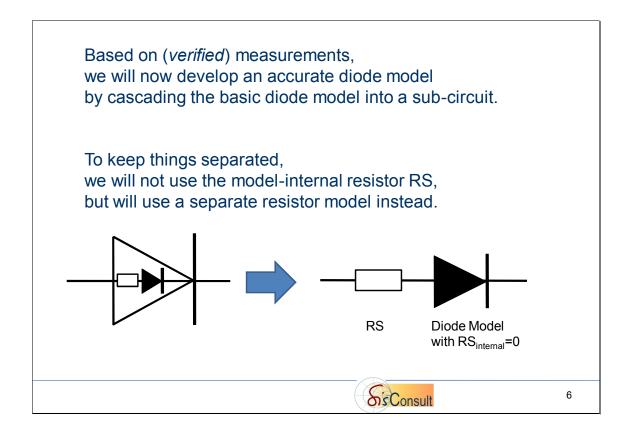

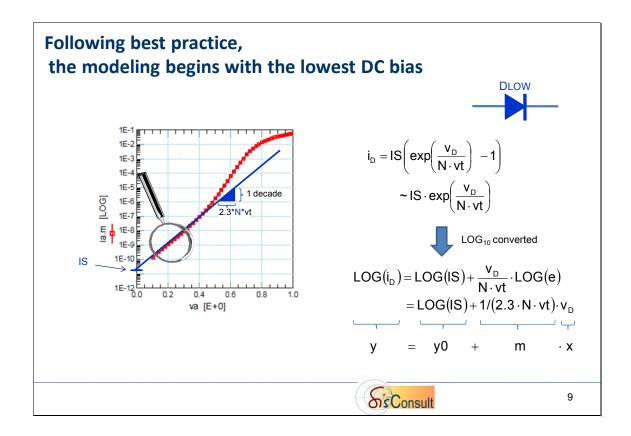

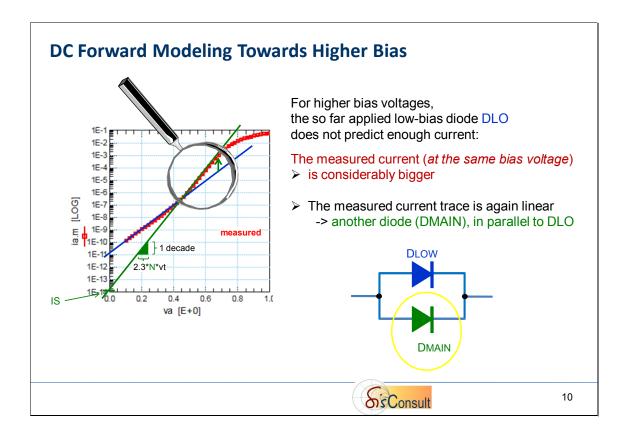

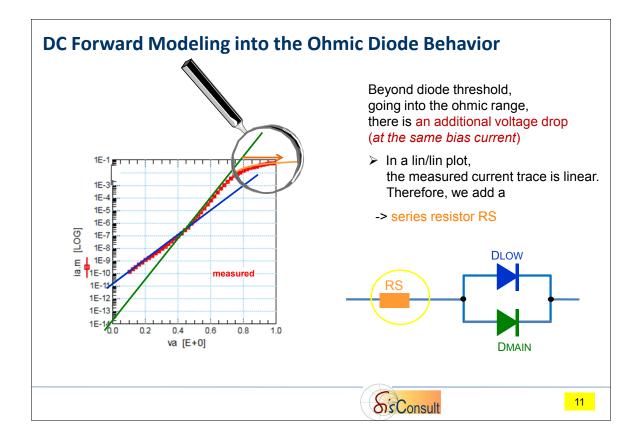

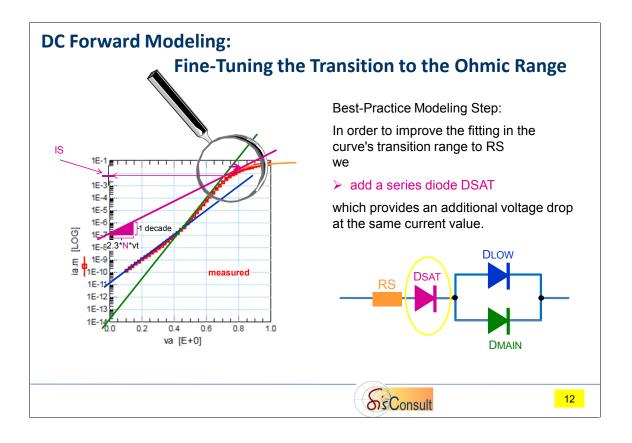

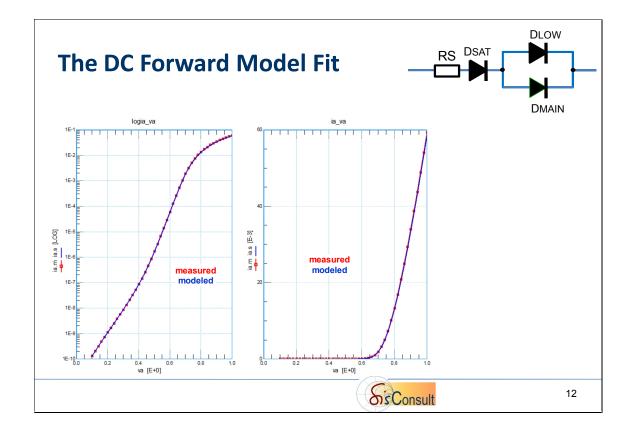

## **DC Forward Modeling**

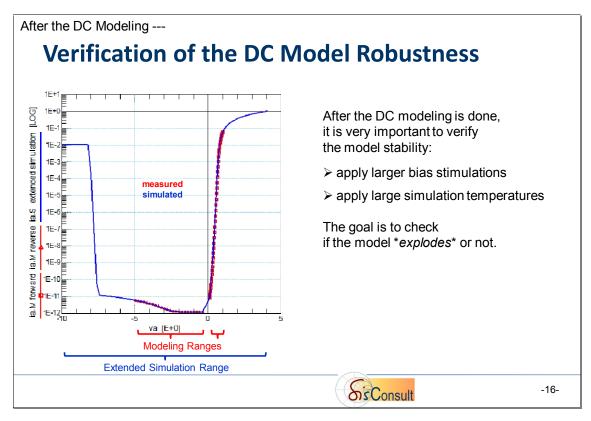

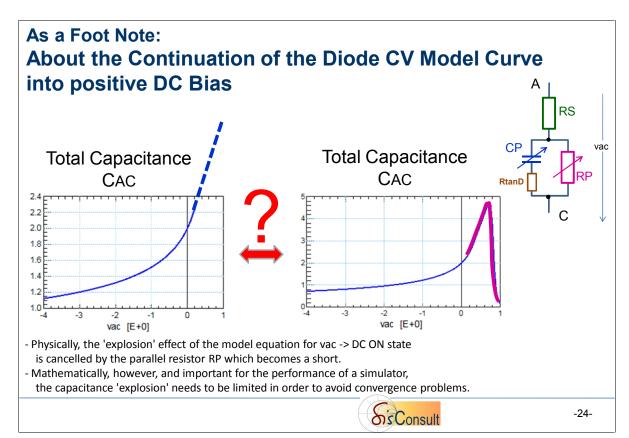

Background: in large-signal RF and in time-domain simulations, the simulator will apply biases which may exceed the modeling range, in order to find a solution for the given modeling problem. If the model would explode, the simulator would go into error state.

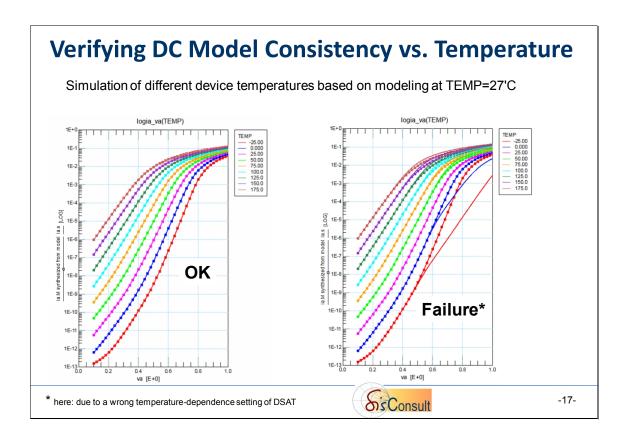

To verify the so far obtained DC model, a prediction simulation of the device behavior at different temperatures is applied to check for abnormalities:

-> expected is a smooth increase of the current with temperature.

The failure shown above on the right is due to an overlay of the wrong temperature-dependence of DSAT.

By switching-off the temperature effect of this 'fitting diode', we obtain the correct behavior as shown on the left.

# **CV Modeling**

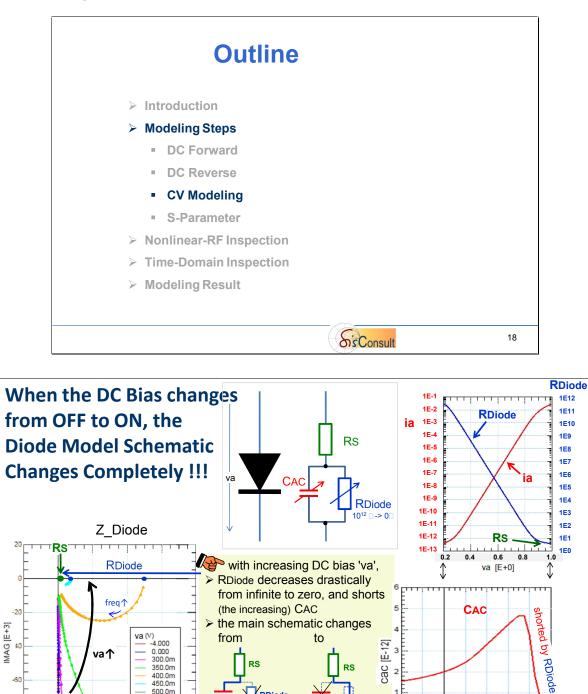

An interesting effect of the bias-dependence of the diode schematic is the change from a mainly series schematic (CAC & RS) for negative DC bias, via a mainly parallel schematic (CAC & RDiode) around threshold, to RS alone at max. positive DC bias (when RDiode is shorting the capacitance CAC).

horted

by RDiode

va > Diode Threshold

RDiode

shorted

by CAC

va < Diode Threshold

400.0m 450.0m

500.0m

600.0m

800.0m 1.000

60

**freq**↑

40 REAL [E+3]

freq

-60

-80

-100 L

cac 2

Sconsult

-0.4 -0.2

0.2 0.4

va [E+0]

0.0

0.8

1.0

-20-

0.6

RDiode

Note: In the plot Z Diode, the end point of all traces for all DC biasings and for infinite frequency is Z=RS.

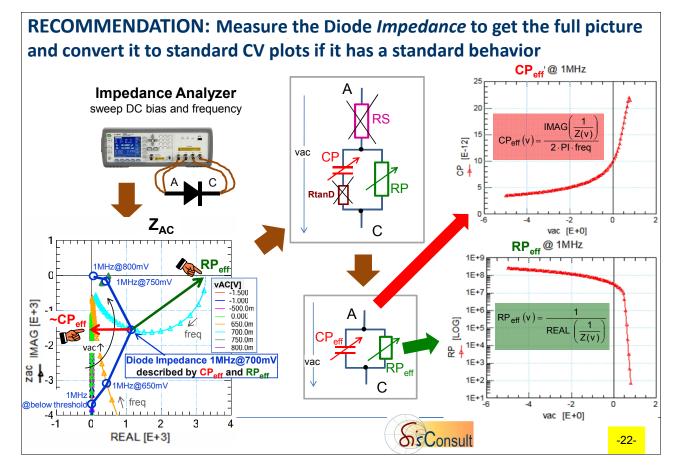

For the CV measurement, an Impedance Analyzer is applied. The stimulation frequency is usually set to 1MHz, the RF signal level is kept at its default value, and the DC bias is swept.

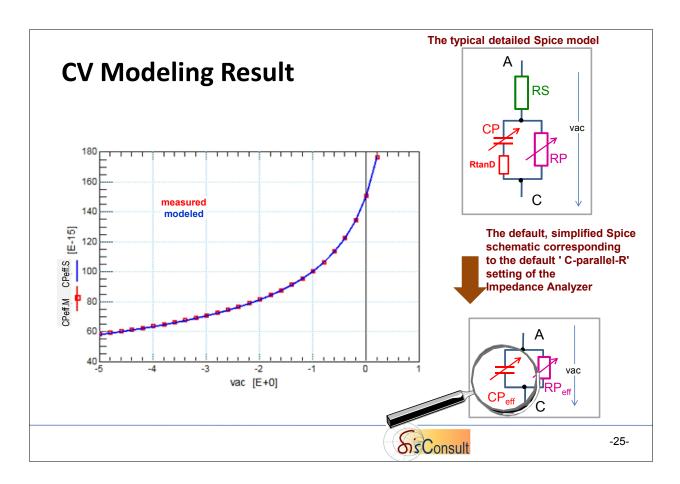

Furthermore, most modeling engineers keep the instrument's default measurement setting what means that the measured impedance, independently how complex its Spice schematic might be, is interpreted and displayed as a capacitance (CP) <u>in parallel</u> with a resistor (RP). And usually, only the capacitance measurement result is applied for device modeling, as shown above on the upper right.

However, for a diode, with its bias-dependent impedance change from OFF to ON, this default measurement neglects the <u>series</u> resistor RS and neglects also the usually present capacitor loss, represented by a resistor RtanD <u>in series</u> with the capacitor (see above). And this simplification explains why the measured capacitance and resistor curves may become frequency-dependent. Modeling engineers then usually apply lower measurement frequencies to avoid this.

A best-practice recommendation is, to measure the impedance <u>without</u> any simplifications. Then, inspect the Impedance Plot trace and identify the underlying Spice schematic. This will enable to identify the effect of RtanD, and consequently, a more precise Spice schematic to be modeled.

## Notices:

## RF Signal Power Level:

It is strongly recommended to control the applied RF signal power, and not to simply keep the instrument's default value which is often too big, especially for CV curves with a big change in slope. In such a case, a too big AC signal may change the DC biasing: the measured capacitance value is the mean value of the capacitances <u>around</u> the bias point.

The procedure to identify the maximum applicable RF signal level is simple:

Start with a low AC signal of e.g. 10mV, and perform a measurement. Then re-perform the measurement, but with an increased RF signal value. Compare with the previous measurement result. If both are the same, you can further increase the signal level (in order to obtain a better signal-to-

noise ratio) until you see a change in the measurement result. Then, keep the signal level which did not yet affect the measurement.

## > What to do with device pins not connected to the measurement

If your diode also has a 3rd connection (e.g. the wafer bulk), connect it to the shielding of the impedance analyzer's BNC connectors. Due to the measurement principle of today's impedance analyzers (balancing bridge), stray capacitors from Anode or Cathode to Bulk will not be included by the measurement (i.e. added to the desired Anode-Cathode-Capacitance).

#### A recommendation for experts:

For a precise Spice model of a diode, it is recommended to measure the diode impedance, with the frequency as the first sweep, and DC bias as the second, and to display the complex impedance in a Real/Imaginary Plot, as shown below. From the impedance traces, a detailed Spice model can be derived, which is often much more complex than just a single, bias-dependent capacitance.

From such an impedance measurement, a simple conversion of the real and the imaginary part of the bias-swept (and default-1MHz single-frequency) diode impedance Z into ' $CP_{eff}$  parallel to  $RP_{eff}$ ' can be applied by the modeling program (see the formulas above) and we are back with the conventional CV modeling.

But with the advantage

- > that we have a better picture of the real diode impedance characteristic,

- and that we have impedance measurements available if a more complex modeling might be required later.

From the CV-plot, the Spice parameter CJO is directly the y-intercept, M is the slope in reverse DC bias, VJ the 'explosion point at positive bias, and FC\*VJ the linear continuation of the Spice model

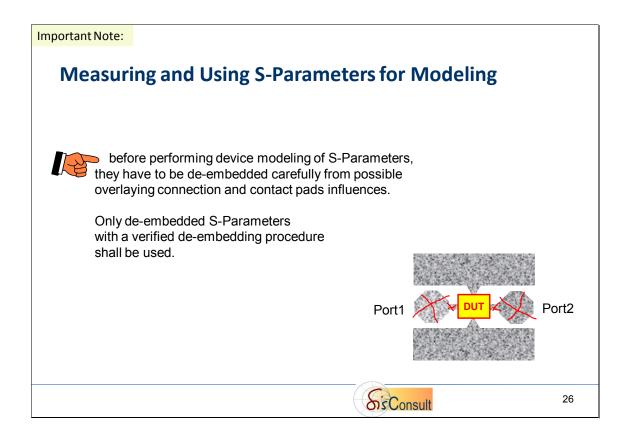

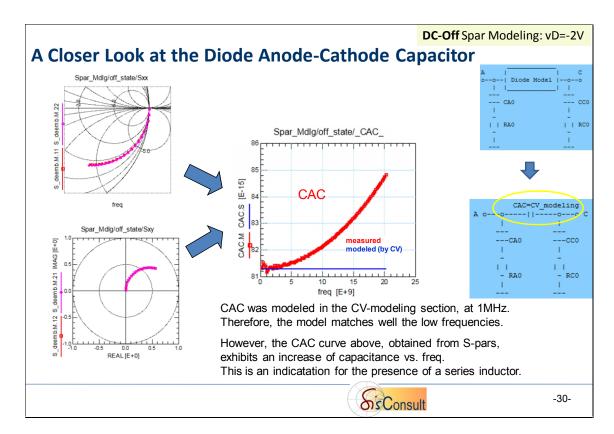

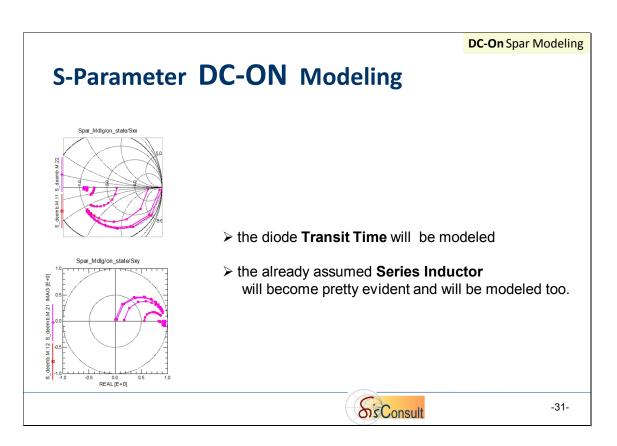

## **S-Parameter Modeling**

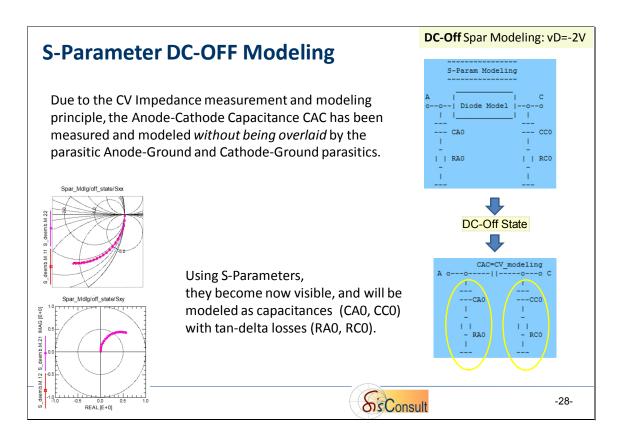

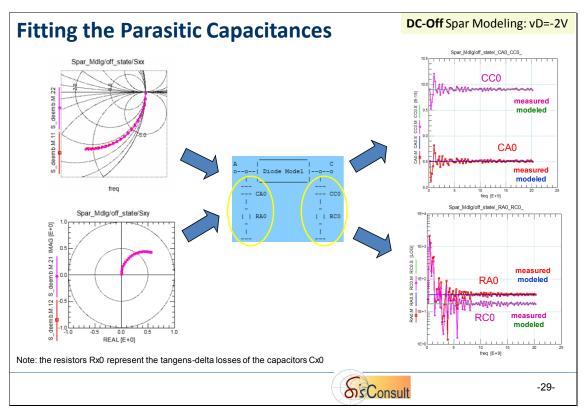

#### How to obtain the component values vs. freq:

1. Transform the de-embedded and verified S-parameters to Y-parameters

```

2. calculate Admittances of PI Schematic:

Yxy = 0.5 * (Y.12+Y.21)

Y10 = Y.11+Yxy

Y20 = Y.22+Yxy

Y12 = -Yxy

3. convert to Impedances

Z10 = 1/Y10

Z20 = 1/Y20

```

Z12 = 1/Y12

```

4. calculate PI Schematic elements

```

```

CA0 = -1/(IMAG(Z10)*2PI*f)

RA0 = REAL(Z10)

CC0 = -1/(IMAG(Z20)*2PI*f)

RC0 = REAL(Z20)

CAC = -1/(IMAG(Z12)*2PI*f)

RAC = REAL(Z12)

```

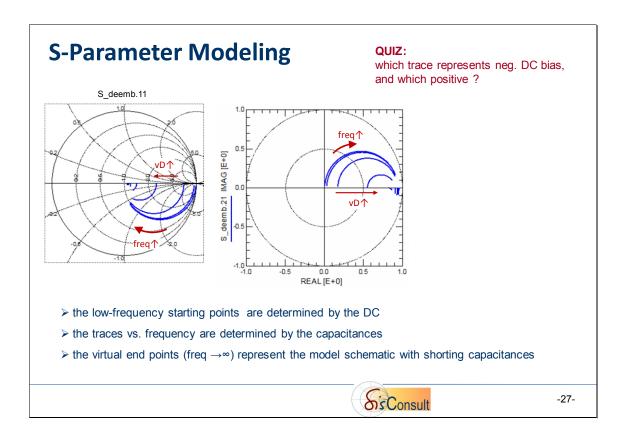

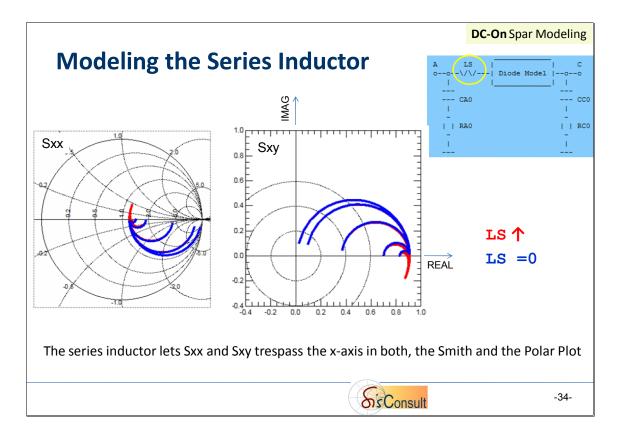

A note about the traces of Sxx:

-> If there was no parasitic CAO nor CCO at all, the traces of Sxx in the Smith Chart would start at the very right, at infinite Ohm (as it does), but end close to the center of the Smith chart for infinite frequency (the diode model itself will be RS), and we see the 50 Ohms of the opposite NWA port. -> With CAO and CCO present, and no resistors in series with CAO and CCO, the end-point for infinite frequency would be at zero Ohm (the very left in the Smith Chart).

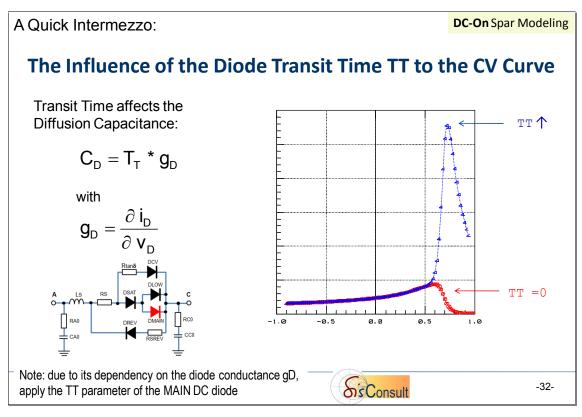

## Note:

The plot above is obtained from an S-parameter simulation, converted to CV. The additional 'explosion' of the CV curve at diode threshold, due to the transit time TT, multiplied by 'exploding' diode conductivity gD, is clearly visible. The collapsing total capacitance towards further forward biasing is due to the shortening of Space Charge and Diffusion Capacitance by the internal diode ON-state resistance ( $\sim 0 \Omega$ ).

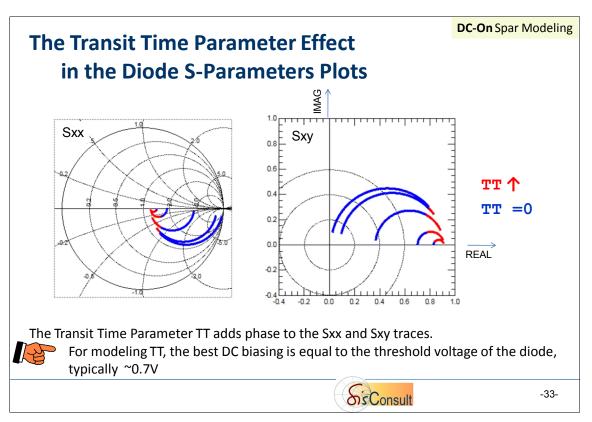

Note: for TT -> infinite, the end point of the Sxx and Sxy traces will be the x-axis in both, the Smith and Polar plot.

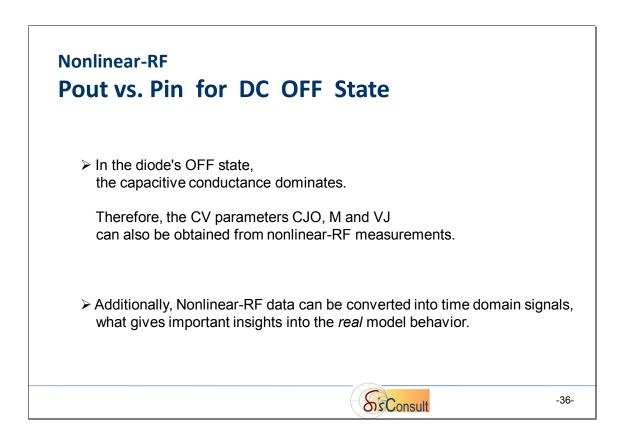

## **Nonlinear-RF Inspection**

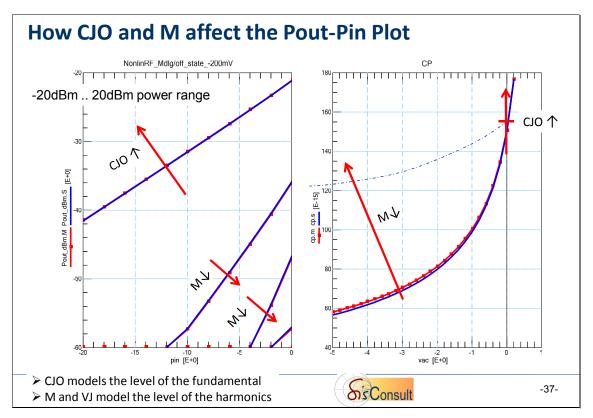

Note: the lower the parameter M becomes, the flatter, i.e. the more linear, the CV trace becomes.

-> A more linear characteristic means less harmonics: the distance between fundamental and harmonics increases.

Note: in the Input Trajectory (iD vs vd), above on the right, watch how far the increasing RF signal can rotate around the DC bias point and extend into the beginning ON state of the diode.

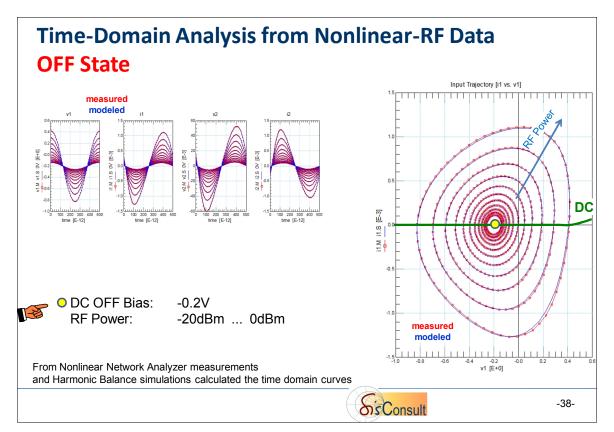

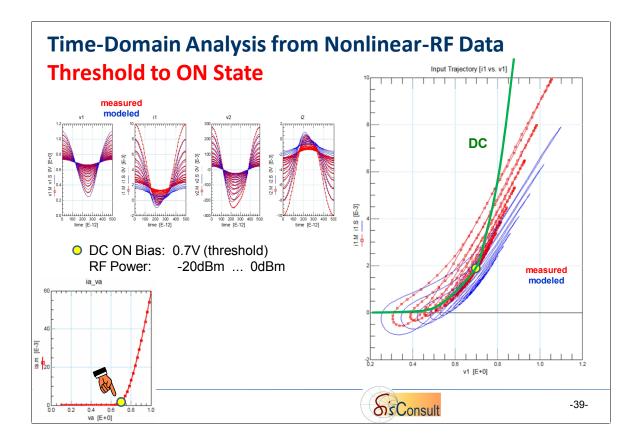

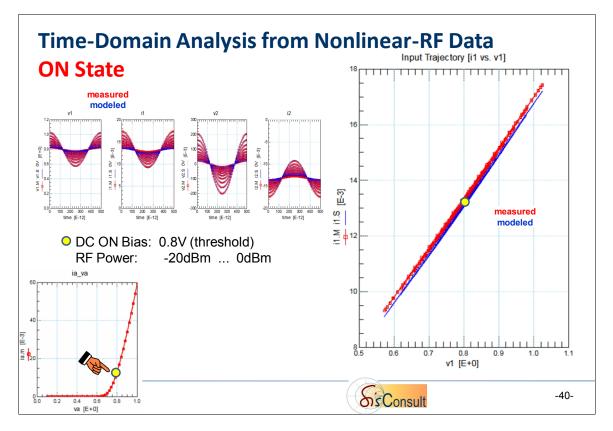

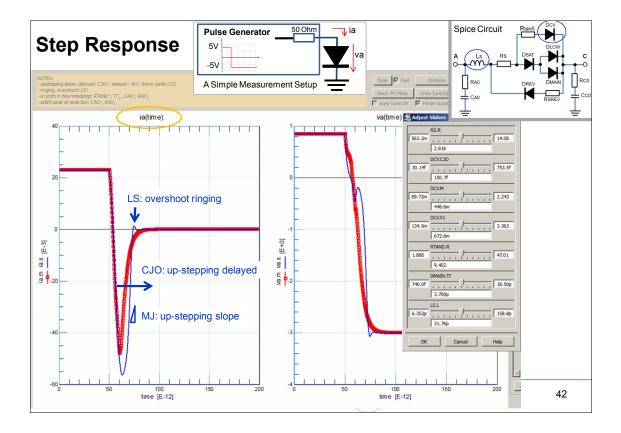

# **Time-Domain Inspection**

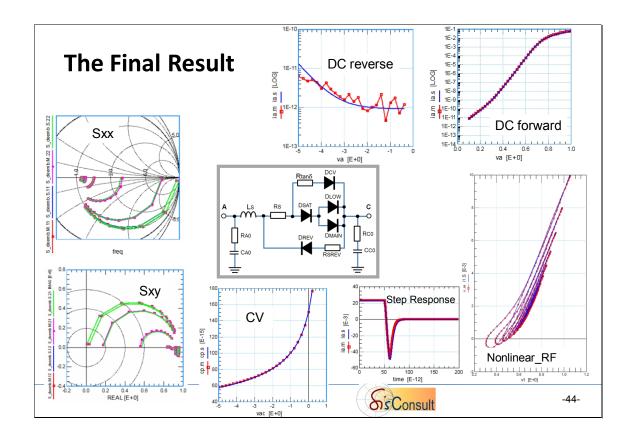

# **Modeling Result**

| .SUBCKT Diode_Modeling A=1 C |          | Spic         | e Ne    | tlict    |              |          |

|------------------------------|----------|--------------|---------|----------|--------------|----------|

| LS.L I II 2.000E-011         |          | Spic         |         | list     |              |          |

| *forward DC modeling         |          |              |         |          |              |          |

| RS.R 11 111 2.927            |          |              |         |          |              |          |

| DSAT 111 12 DSAT             |          |              |         |          |              |          |

| DMAIN 12 2 DMAIN             |          |              |         |          |              |          |

| DLOW 12 2 DLOW               |          |              |         |          |              |          |

| *reverse DC modeling         |          |              |         |          | DCV          | -        |

| RSREV.R 2 21 2.5E+007        |          |              |         |          | Rtano        | - 1      |

| DREV 21 11 DREV              |          |              |         | I        | DLOW         | - 1      |

| *CV modeling                 |          |              |         | A Ls     |              | с        |

| RTAND.R 111 121 1.2          |          |              |         | 0-+ M-+  | ╶═╍╼┲╉┥╗╏┝╼╸ | -0       |

| DCV 121 2 DCV                |          |              |         | RAO      |              | RC0      |

| *parasitic Cs and Rs         |          |              |         |          |              | CC0      |

| CA0.C 1 10 8.511E-015        |          |              |         |          | HONEY        | - 1      |

| RAO.R 10 0 33.76             |          |              |         | <u></u>  |              | <u> </u> |

| CCO.C 2 20 9.903E-015        |          |              |         |          |              |          |

| RCO.R 20 0 16.79             |          |              |         |          |              |          |

| *model cards                 |          |              |         |          |              |          |

| .MODEL DLOW D IS=9.235E-13   | N=1.829  | CJO=1E-18    |         |          |              |          |

| .MODEL DMAIN D IS=3.007E-15  | N=0.9797 | CJO=1E-18    | BV=10   | IBV=1E-6 | TT=3.314E-12 |          |

| .MODEL DSAT D IS=0.004002    | N=0.536  | CJO=1E-18    |         |          |              |          |

| .MODEL DREV D IS=4.378E-15   | N=24.31  | CJO=1E-18    |         |          |              |          |

| .MODEL DCV D IS=1E-25        | N=2      | CJO=1.51E-13 | M=0.452 | VJ=0.675 | FC=0.5       |          |

| .ENDS                        |          |              |         |          |              |          |